To both SBEE Electronic System Design and BEE Antenna Design, all the best.

Midterm evaluation contributes 30% of the overall coursework assessments.

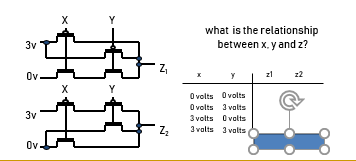

The world is digital, but life is analog..

To both SBEE Electronic System Design and BEE Antenna Design, all the best.

Midterm evaluation contributes 30% of the overall coursework assessments.

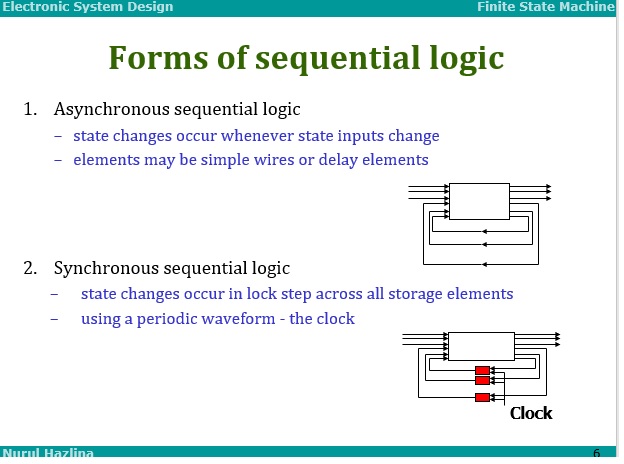

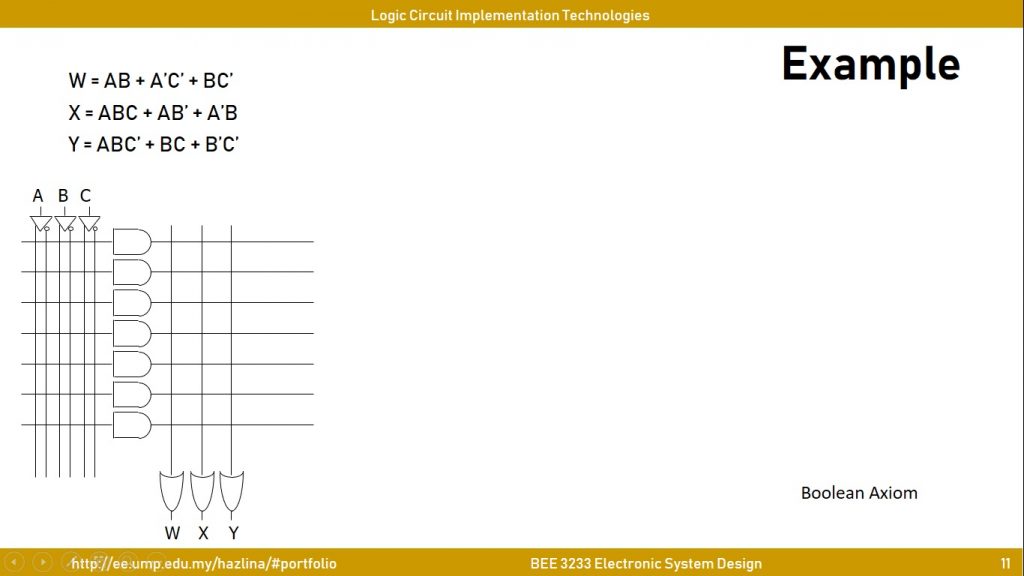

Today’s class covers:-

Today’s topic is on FSM, a way to alleviate the intelligence of a circuit.

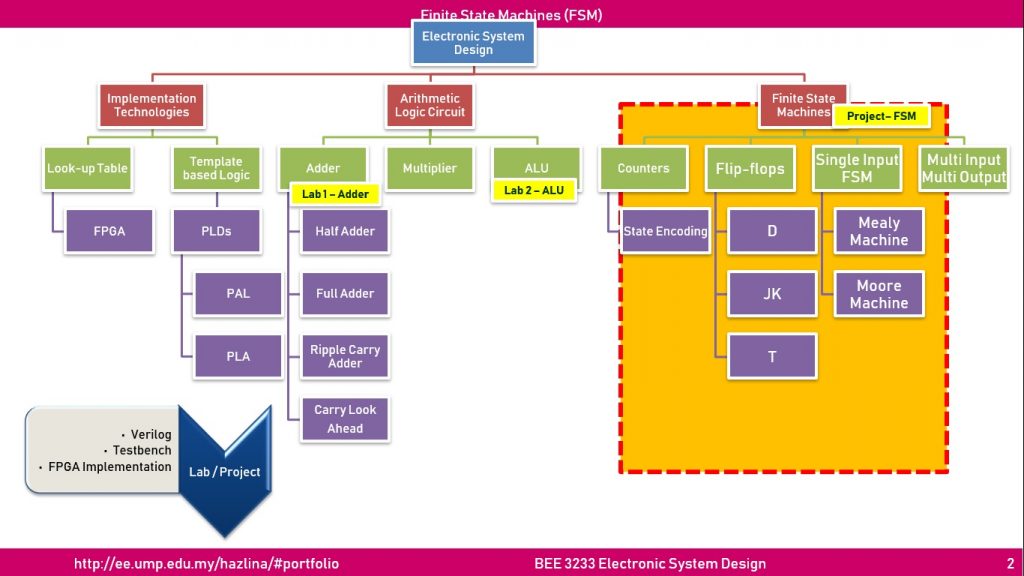

An overview of the course is here

All the best everyone.

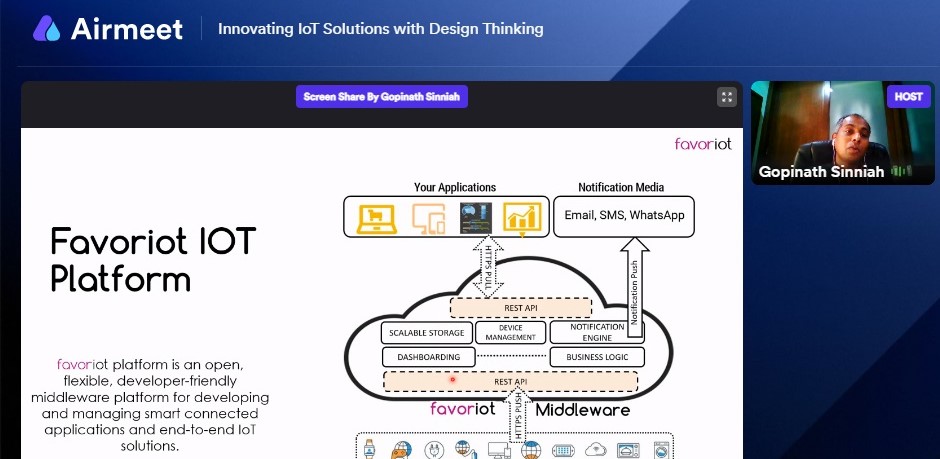

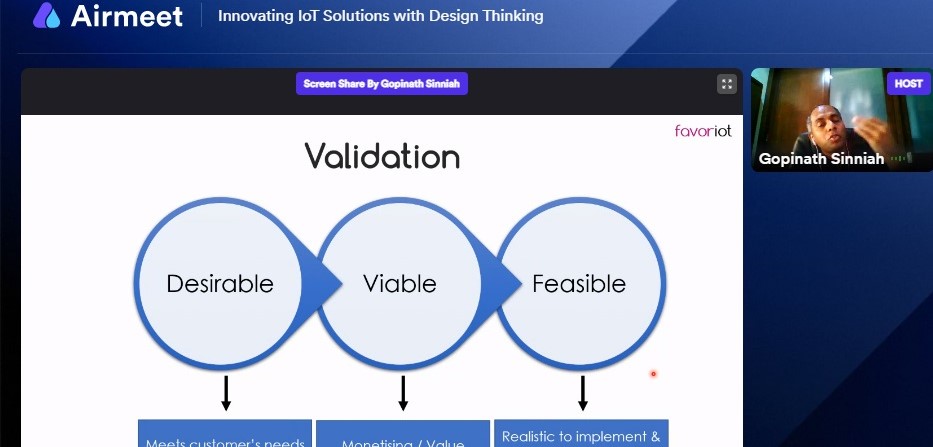

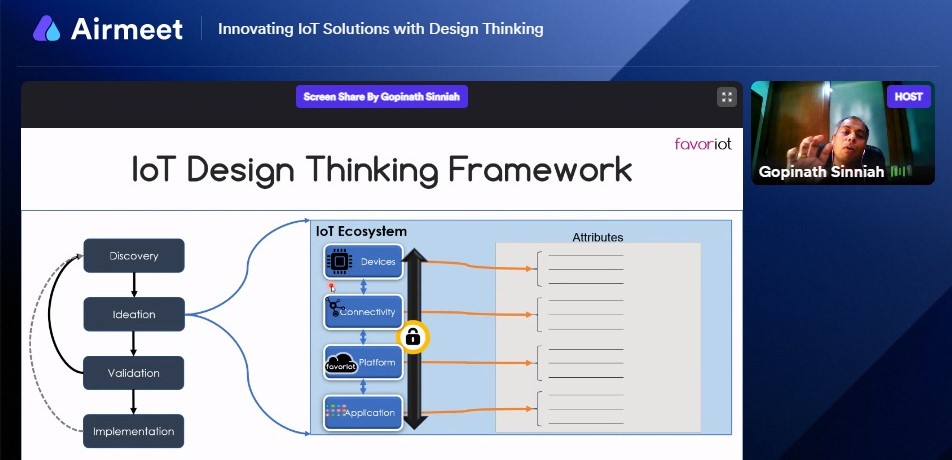

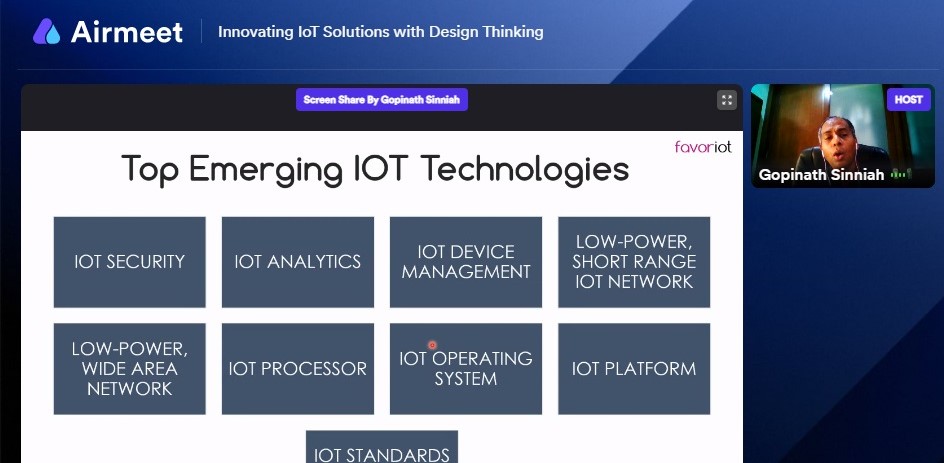

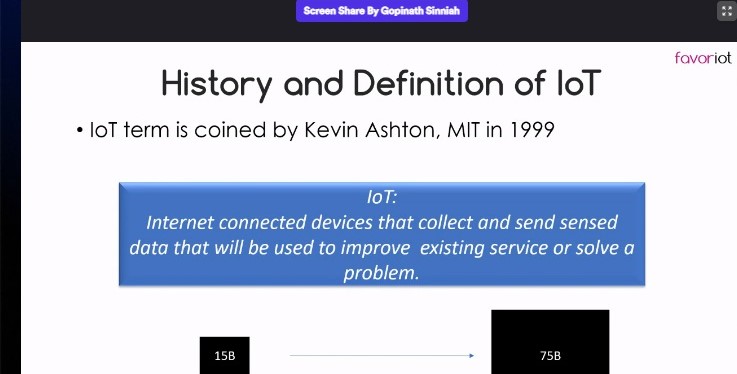

An introduction by FavourIoT.

January 15th 2021

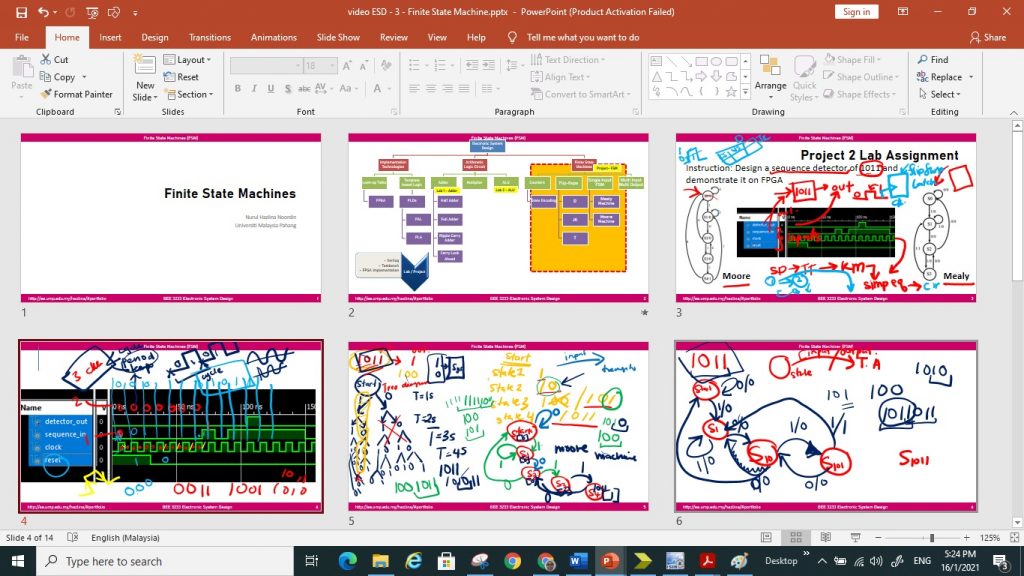

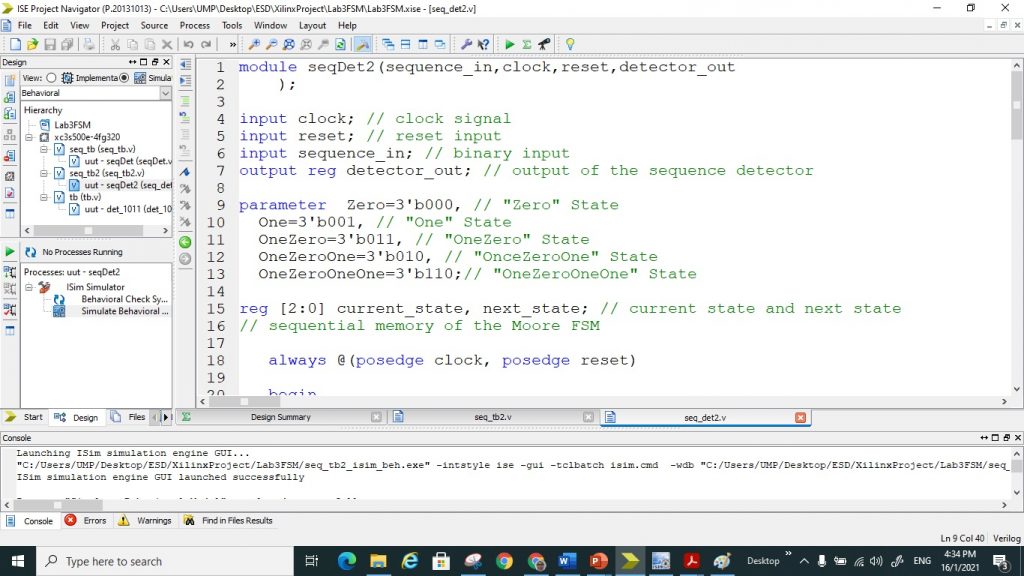

In the final class of Electronic Systems Design, students were assigned to design a finite state machine module of a sequence detector.

Both designs, verilog module and text fixture, are required before it’s implementation onto FPGAs.

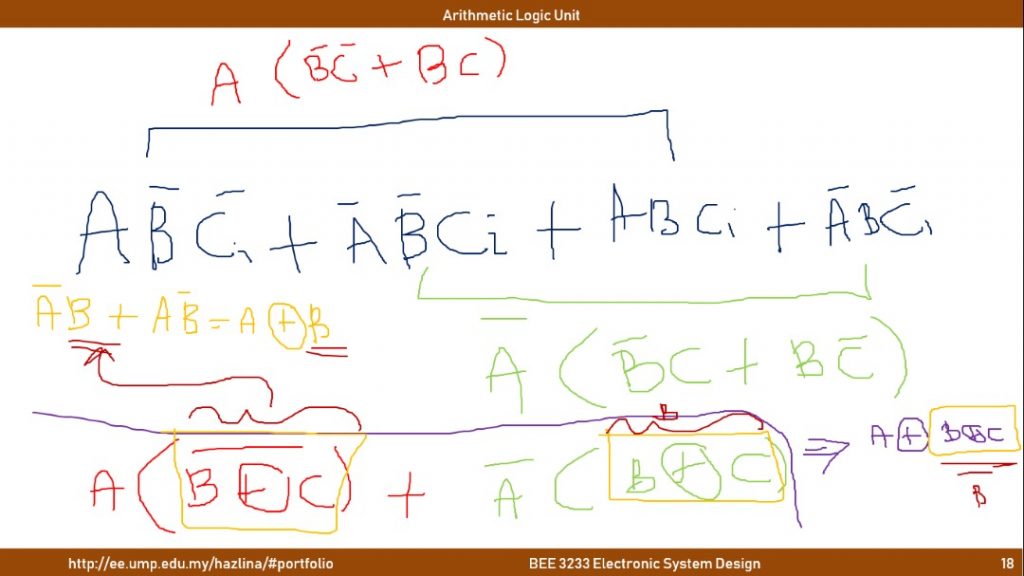

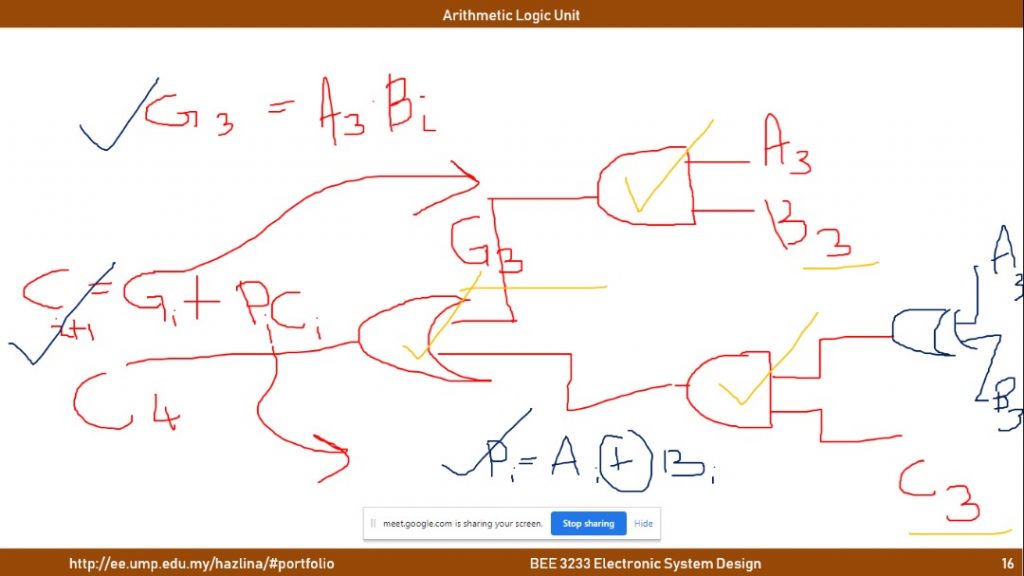

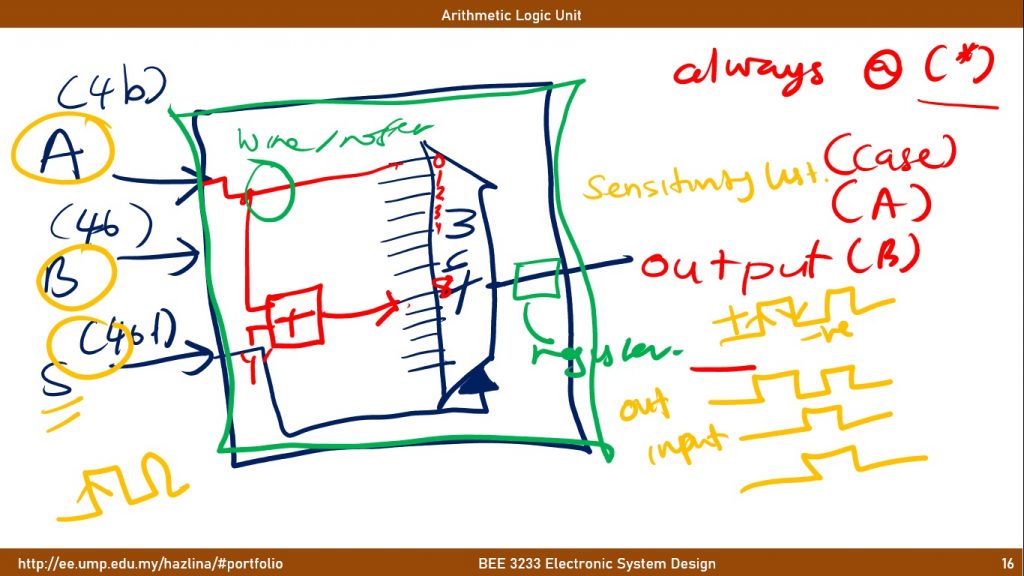

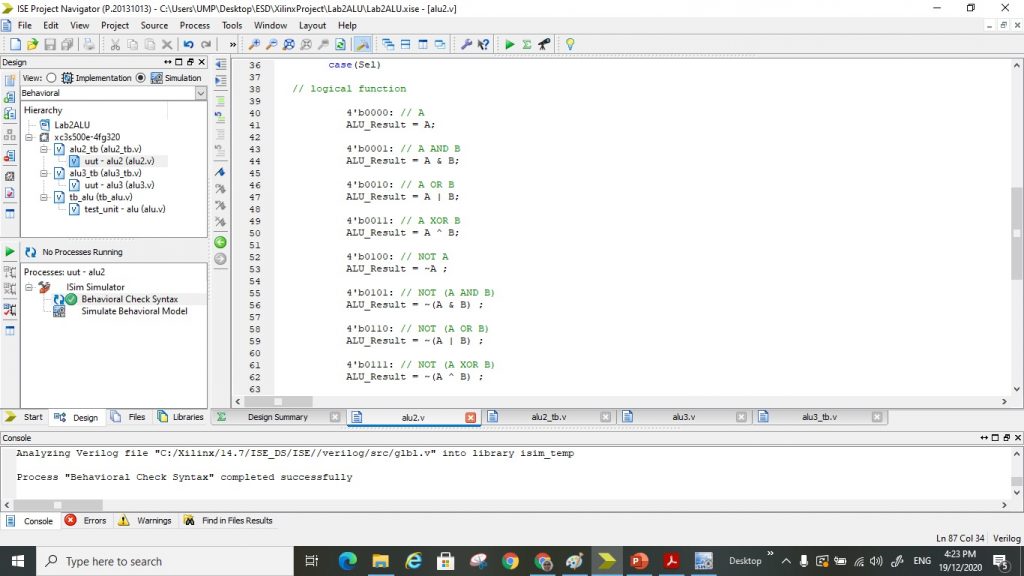

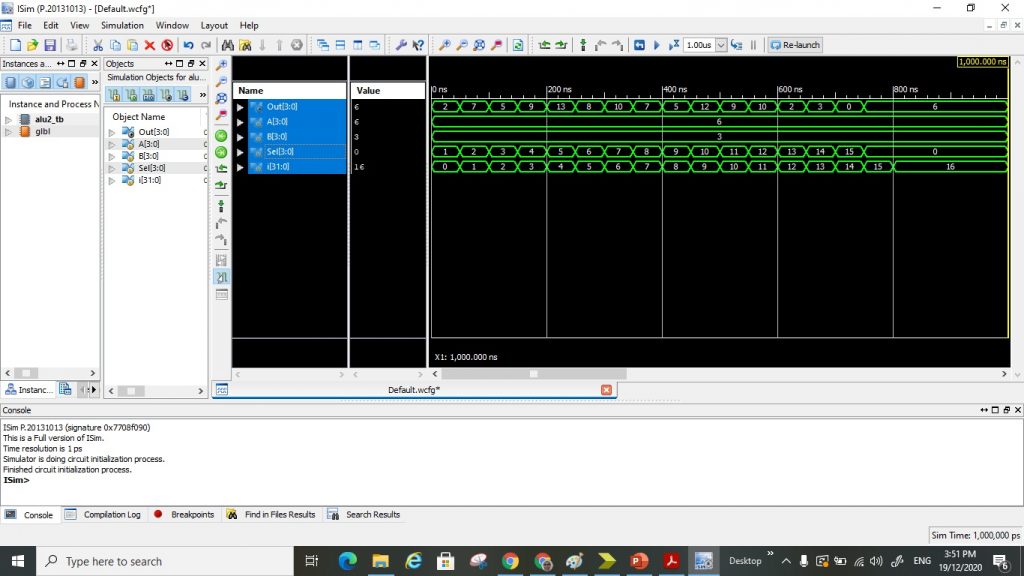

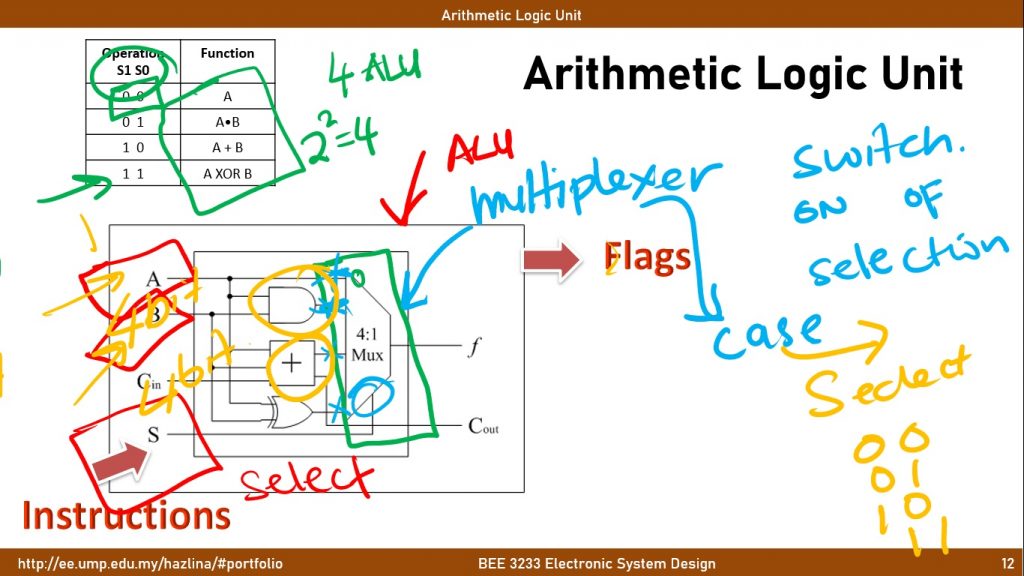

Today’s class focuses on Verilog Design for Arithmetic Logic Unit.

Dec 5th, 2020

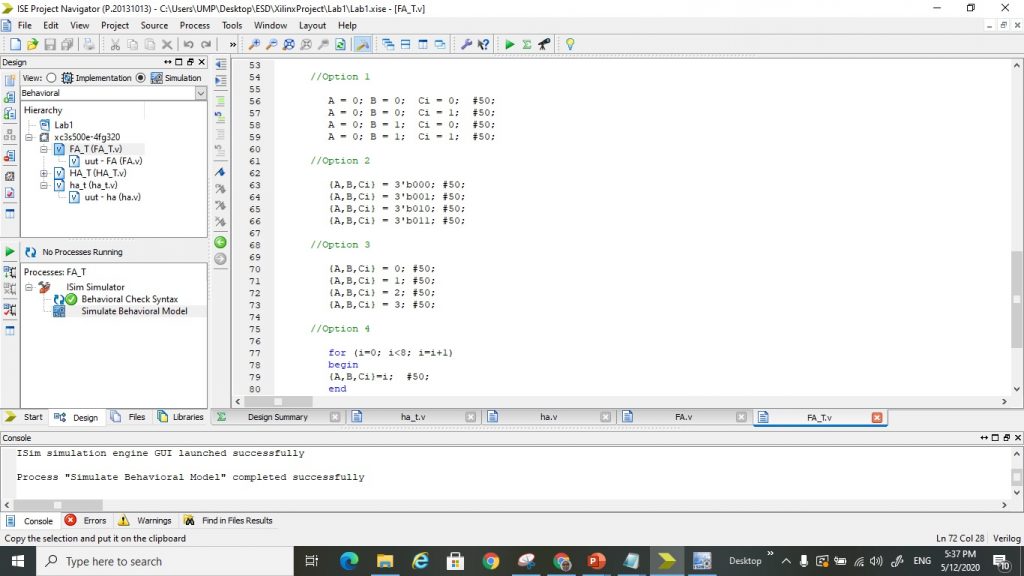

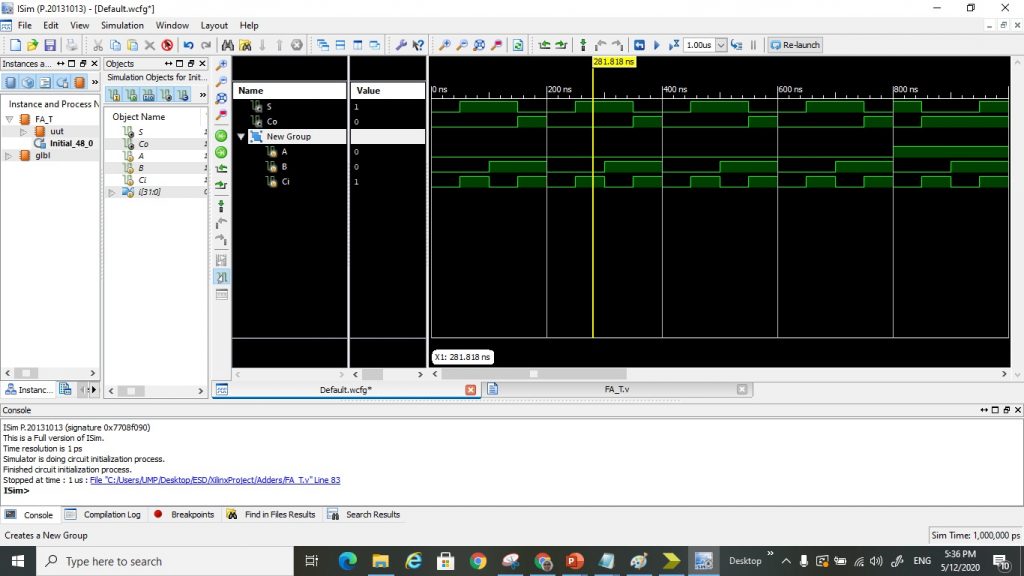

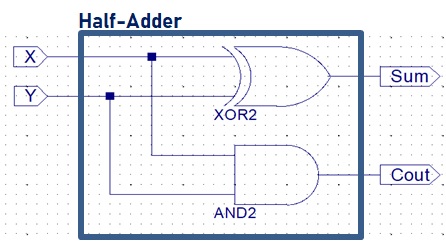

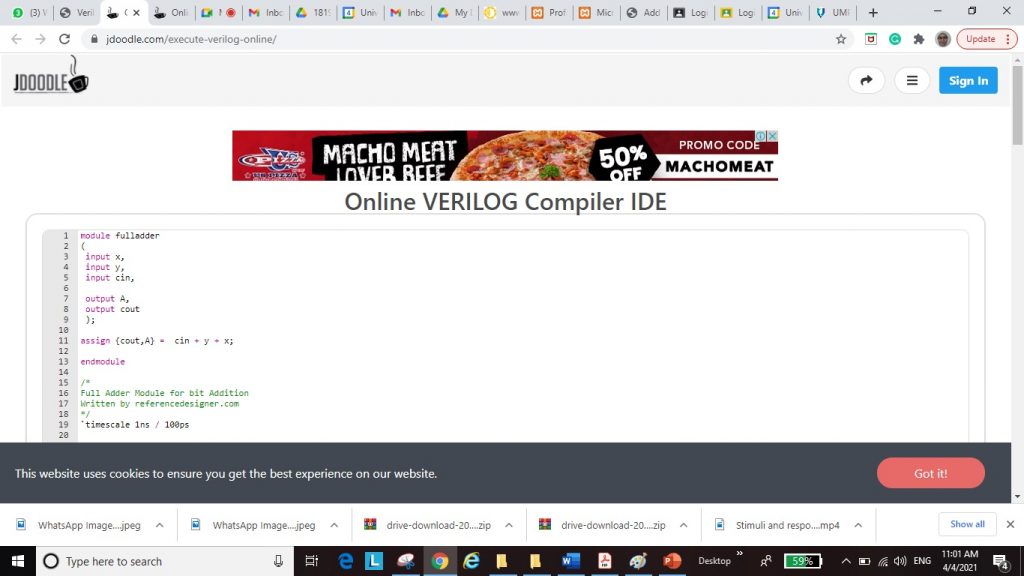

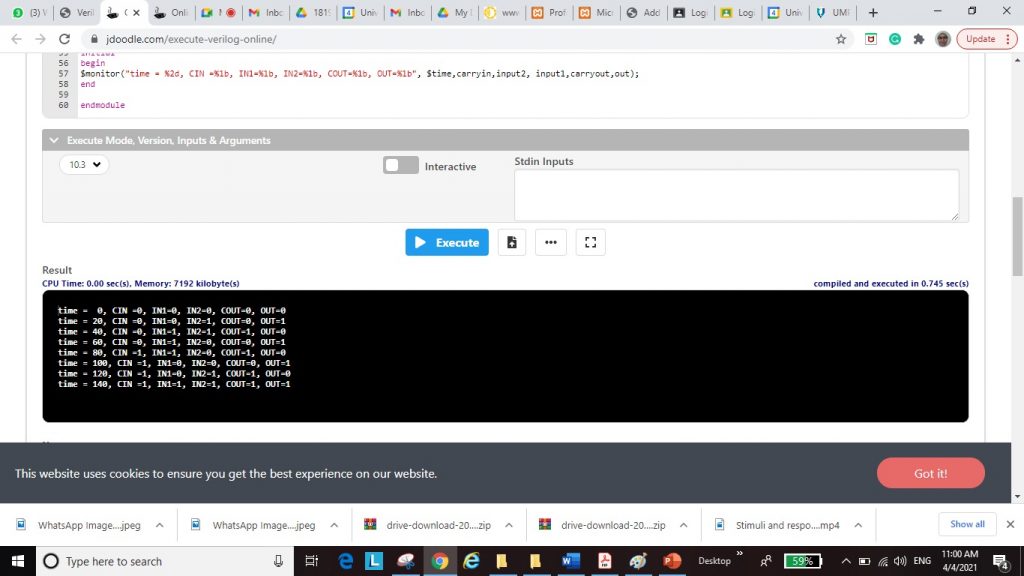

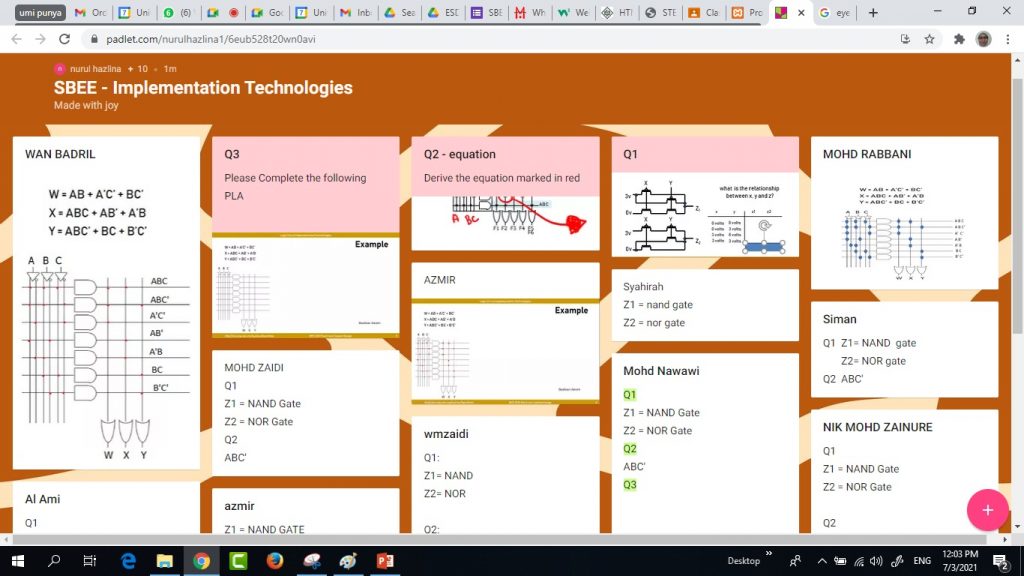

The class focused on Verilog HDL : Syntax, programming and simulation, for both the design module and testbench.

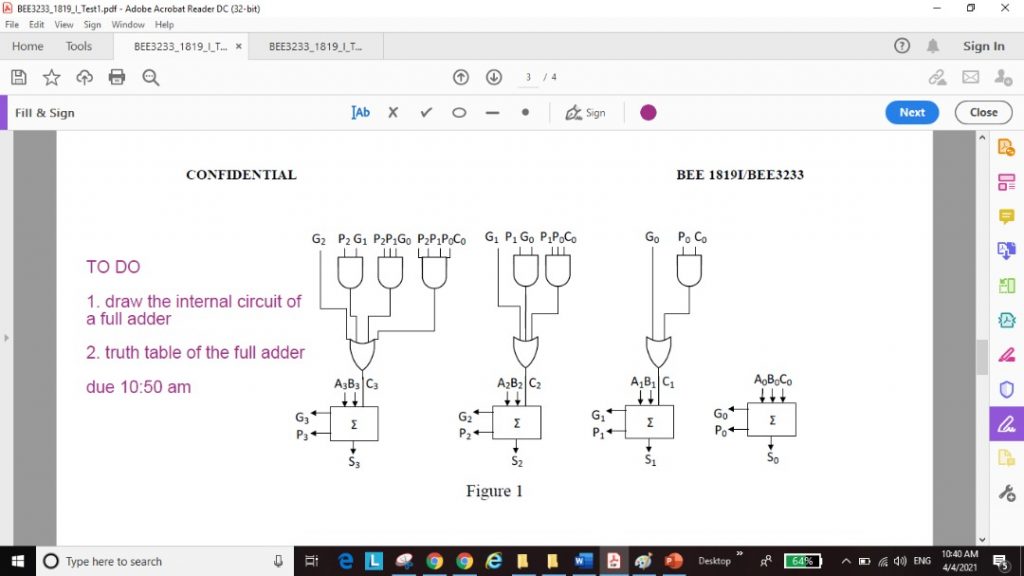

Students gone through half adder, full adder and 4 bit adder HDL design. Not only is it important for students to be able to describe the circuit using Verilog, the must as well be able to translate the simulated waveform as to verify the functionality of the designed digital module.