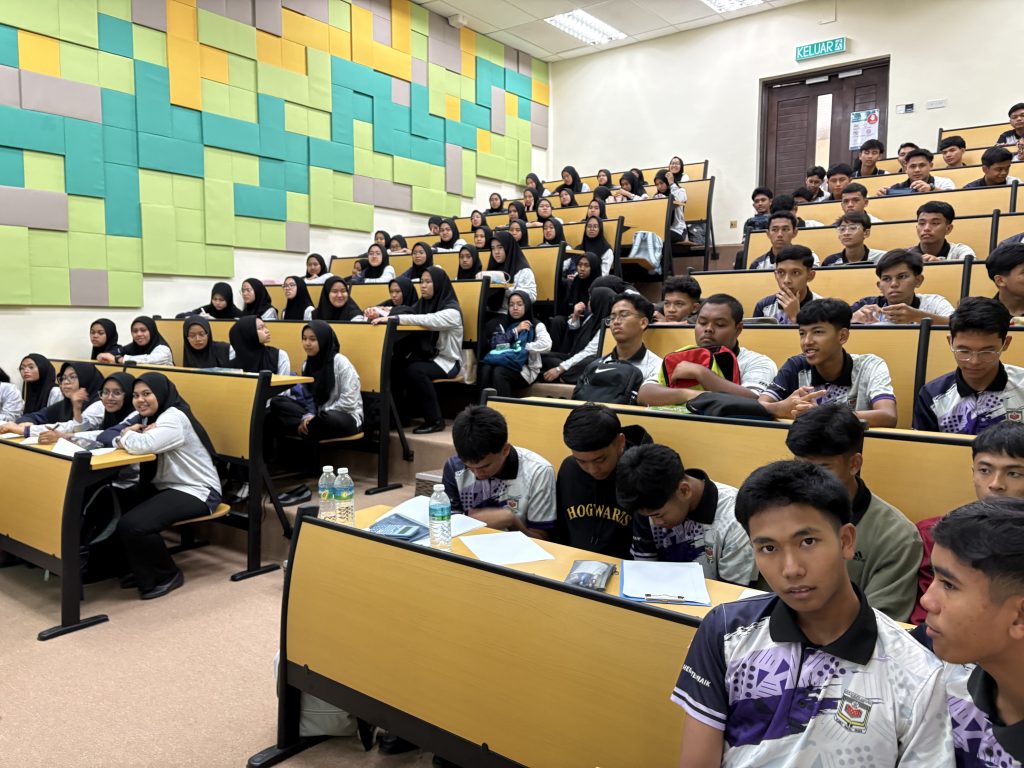

Yesterday, I attended InECCE 2025, a conference organized by the Faculty of Electrical and Electronics Engineering at UMPSA. The session was a meaningful platform to showcase the innovative works of our undergraduate students, particularly their final year projects (FYPs).

In total, five papers were presented, each highlighting a unique research direction that combines embedded systems, sensor integration, microcontrollers, microcomputers, and data analytics. The projects not only reflect strong technical execution but also the students’ growing ability to communicate their findings in a professional setting.

1. Design and Implementation of Circularly Polarized Antenna for CubeSat Applications

This project focused on developing a circularly polarized antenna tailored for CubeSat communications. Antennas of this type are essential to ensure reliable signal transmission regardless of satellite orientation. The work demonstrated solid grounding in antenna theory, simulation, and hardware prototyping, bridging theory with practical space communication requirements. IEEExplore

2. Image Recognition System for Pico-Satellite Earth Surface Analysis (50–75 m) – Amin

A pico-satellite imaging system was designed to perform image recognition at resolutions of 50–75 meters. The project involved integrating cameras with processing units, and developing algorithms for Earth surface feature detection and analysis. Such a system has strong potential for applications in environmental monitoring, agriculture, and disaster assessment. IEEExplore

3. Human-Robot Interactive Miniature Robot – Gan

Using the UMP STEMbot, a two-wheel miniature robot, this project explored human-robot interaction. By programming the robot to respond to commands and adapt to environmental feedback, the students highlighted applications in education, assistive robotics, and interactive learning platforms. The work required programming microcontrollers to interface with sensors, actuators, and wireless communication modules. IEEExplore

4. Navigational System for Miniature Robots – Kiren

This project also utilized the STEMbot, focusing on building a navigation system for autonomous mobility. By integrating infrared, ultrasonic, and IMU sensors, students enabled the robot to avoid obstacles, follow paths, and optimize its movement. The project served as a practical example of applying control systems, embedded programming, and robotics algorithms in real-world scenarios. IEEExplore

5. Integrated Data Acquisition and Environmental Analytics in Pico-Satellite Systems – Zharif

In this work, a data acquisition and analytics system was designed for a pico-satellite, the STEM Cube. The system collected environmental parameters (e.g., temperature, humidity, radiation levels), stored them in a database, and processed the data for visualization and decision-making. This project required students to master both hardware sensor integration and software development for analytics and visualization. IEEExplore

Beyond Hardware – Communication Skills Matter

It has always been a practice in UMPSA STEM Lab’s project supervision to develop a tangible projects (involves hardware – circuit design and development), simulation and analysis, as well as the presentation and paper-writing skills. Producing technical hardware (embedded systems, robots, satellites) is one challenge; communicating the work through IEEE-style papers and oral presentations is another. Both are equally critical in preparing students for industry and academic research.

That is why I emphasize to my students:

- Build the system – design, test, and validate the hardware/software.

- Code, simulate and analysis – code and program micro controllers / microcomputers / FPGAs

- Communicate the system – write a paper, prepare figures, and present findings confidently.

Conferences like InECCE 2025 in Kuantan provide exactly this type of exposure, bridging classroom learning with professional dissemination.

I look forward to bringing my current and future FYP / SDP / URP / PG students to similar conferences, providing them opportunities not only to engage in project-based learning but also to present and publish their work. Such experiences shape them into well-rounded engineers who can both design systems and communicate ideas effectively to wider communities.